# Design and Development of Burden Lenient Network On-Chip Using FPGA

S. Ravichandran

Department of Computer Science, Annai Fathima College of Arts & Science, Madurai, Tamil Nadu, India. siasriravi@gmail.com

Abstract - This Network on-chip (NoC) stands a novel structuring correspondence convention. It makes я correspondence between the on-chip centers. It has been proposed as one of the interconnect answers for future System on-chip (SoCs). This paper presents a disengaged/online concurrent compass based verifiable individual test (check BIST) methodology for a Network-on Chip (NoC). The proposed designing contains a special yield cell and an Embedded Test Core (ETC) as its test source. The ETC plays out a static stream control and a determined typical power use control during the proposed test instrument. This shows the arranging and execution of a totally special pipeline circuit-changed change to help ensured throughput. The circuit-traded switch, supported a backtracking testing way course of action, works by an upwelling-facilitated trend-pipeline method. This control can reinforce a numb and live-latch gratis one of a kind way arrangement conspire and can accomplish high transmission capacity, high territory and vitality productivity. The proposed BIST strategy empowers fast go/off limits BIST, with minor additional region inside the NoC itself. Chip configuration is turning out to be progressively correspondence bound rather than calculation bound. In this paper the test planning issue is likewise tended to for such NoC-based SoCs. We acknowledge a crossbreed BIST approach, where test sets of individual focuses are made out of pseudorandom and deterministic test courses of action and, instead of various other arranging moves close, not treated as mystery components. This work likewise presents two more procedure called N-identify test unwinding and half and half calculation to improve the presentation of the framework.

Index Terms – BIST, LFSR, Network on Chip (NoC), SoC, Fault Lenience and FPGA.

#### 1. INTRODUCTION

In the region of Embedded Systems, there's a longing to make Frameworks On-Chips'(SOC's), the usage and mix of numerous PC parts or whole electronic frameworks (microcontroller, memory squares, clocks, voltage controllers, and so forth.) on a solitary chip. In any case, a replacement and continuously notable research field which keeps an eye on a portion of the concerns of amazing correspondence between on-chip sections Network-on-Chip (NoC) plan, attempts to bring compose specific frameworks to on chip exchanges, so as to improve execution over ebb and flow transport based frameworks. Essentially, plan space investigation pro Systems-on-Chip (SoCs) consumes primarily tended to those reckoning parts of that issue inside the current framework. In any case, as both the measure of segments on one chip and their presentation despite everything increment, the arranging of the correspondence design assumes a significant job in characterizing the region, execution and vitality utilization of the general framework. Moreover, worldwide interconnects cause extreme on-chip synchronization mistakes, capricious postponements and high force utilization [1].Hence Networks-on-Chip have been proposed as an elective correspondence stage fit for giving interconnections and correspondence among On-chip centers, taking care of execution, vitality utilization and reusability issues for mammoth incorporated frameworks [2]. NoC is a promising option in contrast to old style transport based and highlights point correspondence designs.

System on-chip is additionally used to structure an on-chip control/control toward powerfully bolster (rigid) ensured quantity [3] below the requirements of intensity, timing, and zone. NoC give ensured administrations, for example, uncorrupted, lossless, requested information conveyance and limited idleness is basic for the proficient development of hearty SoCs. NoC utilizes pipelined time-divisionmultiplexed circuit exchanging, to execute its ensured administrations [4]. However, this TDM method looks concern in that management of tremendous schedule vacancy boards at certified management controls pro dispute able communication [4] and limitation of this guiding size for halt able evidence transfer in that effective paths by an essential approach might rapid quantity debasement in Packetswapped NoCs [5].So path-swapping approach is picked to impart confirmed quantity since of the situation alluring QoS [6] [7] property. After this arrangement, start to finish evidence can be conduit all together by the filled pace of that committed associates with little postponement, no evidence jitter, then concerning a lossless manner.

Ordinarily Built-in-individual test (BIST) is utilized to work out the adaptation to non-critical failure in NoC. Worked Inindividual test (disconnected/on the web) of circuit with examine (filter BIST) accomplishes high shortcoming inclusion with low overhead [9]. Furthermore it doesn't require changing the capacity rationale and doesn't debase framework execution. During worked in singular test (BIST),

the game plan of models delivered by a pseudo-subjective models generator most likely won't give satisfactorily high insufficiency consideration and heaps of models were undetected issues, so some model forms test time [10]. Thus, we reseed and change the pseudo-irregular piece to improve test length and accomplish issue inclusion of 100%. The way that an irregular test set contains futile (non-deficiency dropping) designs, so we utilize equal innovation, including both reseeding and bit adjusting (additionally called design mapping) to expel pointless examples (for example decrease the test time), bringing about short test length.

In that manuscript, that essential wired BIST then BIST constructed indicative methodology [11] are utilized pro that programmable interrelate assets inside FPGAs respectively. That interrelate BIST remains utilized inside this wandering STARs method. This system gives an entire BIST of that programmable interrelate shadowed thru significant standards diagnostics to help re arrangement round this inadequacy pro defect receptive requests respectively. Roving STARs approach takes two sections of CLBs to make a two columns of CLBs to variety of a level STAR (H-STAR)and vertical STAR (V-STAR) in light of the fact that the worldwide interconnect is ordinarily spread into both the vertical and even bearing [11]. Usually flat STAR and vertical STAR sets aside extraordinary effort for filtering in FPGA. In this task the examining time for both H-STAR and V-STAR are diminished to speed up. We additionally utilized a substitution strategy called genuinely mindful N-distinguish test unwinding to downsize the test design age. This method utilizes just 64 test examples to distinguish blames however, though reseeding strategy requires 256 test designs. So it decreases the test time just as it improves the presentation.

## 2. RELATED WORK

The Framework of On-Chip (NoC) plan perspective consumes projected as the possible destiny of that ASIC structure [12]. Adaptation to non-critical failure in NoC is regularly gotten by correspondence design. In NoC correspondences the two significant wellsprings of blunders are crosstalk flaws and delicate mistakes [2] [13]. Previously, it was expected that associations can't be influenced by delicate blunders in light of the fact that there was no consecutive circuit included. Nevertheless, when NoCs are utilized, supports and successive circuits are available in the switches, thus, delicate mistakes can happen between the correspondence source and goal inciting blunders. Deficiency open minded methods that once have been applied in incorporated circuits when all is said in done can be utilized to ensure switches against bit-flips. The results show that the effect of those lacks in the SoC correspondence can be horrifying, provoking loss of groups and system crash or unavailability then it proposes and assesses a lot of deficiency open minded procedures applied at switches ready to relieve delicate mistakes and crosstalk flaws at the equipment level. Such strategies depended on blunder revising codes and equipment repetition.

Another technique for adaptation to internal failure in NoC can be accomplished by versatile remapping [14]. The new calculations are regularly wont to powerfully respond and get over PE disappointments in order to deal with framework usefulness. The nature of results is like that accomplished utilizing recreated strengthening yet in essentially shorter runtime.

#### 3. PROBLEM STATEMENT

In this area, the specific idea of framework model is predicated on NoC engineering [15] and in this manner the plan of deficiency open minded NoC switch.

3.1. Network-on-Chip Design

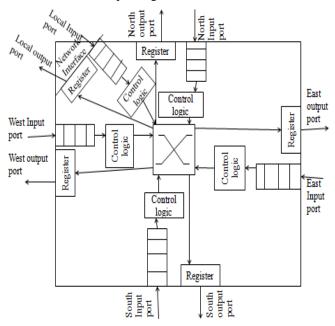

Figure 1 Conventional NoC Router Design

The Network on-Chip otherwise Network-on-a-Chip (NoC or NOC) stands a way toward deals with plan that correspondence subsystem among IP centers voguish a System-on-a-Chip (SoC). NoCs be able to traverse coordinated then no concurrent timer area rationale. NoC relates arranging out theory and procedures to on-chip communication and gets arresting updates over customary crossbar and vehicle interconnection during a standard NoC, every switch consumes five info docks and five yield docks looking at toward the west, east, north, and south, direction similarly like the close by getting ready part. Every docks will associate with extra dock on the adjacent switch by means of a lot of corporeal interrelate ropes (stations) respectively. This

switch's capacity stands to course flits inflowing after every information dock to a fitting yield dock then near the last goals. It comprehend that capacity, the switch remains outfitted by an information core pro every info port,  $a5 \times 5$  various crossbar changes toward divert traffic to that ideal yield docks then essential switch rationale to guarantee accuracy of directing outcomes so appeared within aboveFigure1:

Ordinarily, pro every datum bundle, this comparing mind flit indicates the situation proposed goal. In the wake of inspecting this mind flit, this switch controller method of reasoning desire make sense of which yield course to course entirely the resulting (mass then end) flits related by this information package as demonstrated by the guiding computation applied.

# 3.2 Fault lenient Router NoC design

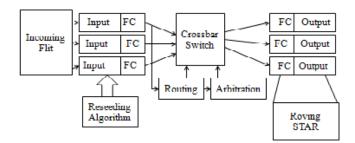

The Fault lenient NoC switch design depends on Backtracking wave pipeline Switch engineering [3].Fault open minded NoC switch is actualized by five double directional docks which remain appropriate designate utilized inside together Mesh and Torus topologies respectively. Nearby is nope check in that plans then the entirety of the information transmissions are placed enthusiastically thru the assistance of handshaking portends respectively. The fourstaged grasp convention devises been utilized in that switch [16]. Figure 2 shows Fault open minded NoC switch.

Figure 2 Conventional Fault lenient NoC Router Design

The switch includes three key units which are effort support, crossbar control, besides coordinating unit. Information cushion is mindful to stow incidentally approaching bounces since contiguous switches whether it has gratis interim. This constraint of data pad in every one of the five docks is five moves (unique support is committed per docks) separately. Every information support comprises a pawn to decide that quantity of got flutters in present bundle. That pawn remains gotten to thru an act segment named slogan extractor which recognizes slogan dance amid others in a bundle respectively. Slogan mainframe remains extra sub-segment of steering part which is capable to handle the approaching parcel's legend. Directing component remains that this fundamental part during this structure. Directing procedure is actualized during this part once a substitution bundle has been gotten. Each info channel can hold one of yield ports in the wake of steering procedure consumes been practiced respectively. The intervention component is exploited toward devote this yield docks by cooperative calculation uncertainty there's very unique solicitation pro an extraordinary yield station. Here different word, thru the benefit of watchfulness replace fragment yield docks stay scattered really done data docks. When directing board fixed that control interfaces, the info port is associated with fitting yield port. The last segment which is crossbar switch is accountable for interfacing all information ports to every one of yield ones respectively. This switch signs of steering element choice unique among yield docks pro an approaching caption dance.

# 3.2.1 Reseeding Algorithm

Reseeding calculation is utilized to upgrade deficiency inclusion in BIST pseudo-irregular testing [17]. The greater part of this effort complete upon reseeding remains predicated upon putting away that stones inside an outer analyzer. Other than its significant expense, testing utilizing programmed test hardware creates the situation difficult toward check this track inside this framework. Thus implicit reseeding [10] strategy is utilized. This method needs nope capacity pro the stones respectively. This stones remain deterministic and encrypted inside equipment, so 100% flaw inclusion can be accomplished. This strategy sources nope introduction above then doesn't modification that main path below check respectively. Worked inside reseeding remains predicated upon extending each stone toward whatever number ATPG designs for example could reasonably be expected. This is not the same as many existing reseeding methods that grow each seed into one ATPG design. A preferred position of implicit individual test is its minimal effort contrasted with outside testing utilizing programmed test equipment (ATE)[17] separately. Now BIST, the on-chip hardware remains incorporated to give check routes then toward break down reaction. Various electronic circuits vield contain discretionary model safe (r.p.r) these lacks this edge that incorporation of quasi-periodic challenging [17] respectively. This r.p.r deficiencies remain defects by little detectable quality (Scarce models recognize them separately). A few strategies are proposed for upgrading the deficiency inclusion accomplished with BIST. These methods utilize an extra piece counter and changing circuit in which deterministic test solid shapes are implanted in the pseudo-arbitrary grouping of bits [8]. The adjusting circuit is included at the sequential yield of the Linear Feedback Shift Register (LFSR) [10] to alter the pseudo-arbitrary piece arrangement with the goal that the helpful examples will be acquired

Reseeding implies stacking the LFSR with a seed that wanders into a pre figured test plan. The activity of the reseeding circuit is as per the following: the LFSR begins running in self-sufficient mode for at some point as indicated by the reseeding calculation. When it's the ideal opportunity for reseeding, a seed is stacked into the LFSR, which at that point returns to the independent mode then on then forward until the ideal inclusion is accomplished. The new seed is in the LFSR. By enacting the select line of a multiplexer, the rationale esteem in the relating LFSR stage is rearranged in reseeding methodology deterministic models are applied after an unpredictable testing to reduce number of the model. The deterministic example are stacked into the LFSR and afterward consumed into the longing designs in the output chain. This procedure reuses some portion of the sweep chain flip-flop in growing the seeds.

In this methodology, discretionary models that don't recognize r.p.r imperfections are mapped to ATPG made 3D squares through combinational basis. The mapping is acted in two stages, the pseudo-irregular examples are distinguished inside the activity, and subsequently the ATPG blocks are stacked inside the subsequent advance. In this, we stacked new seed by placing the LFSR in the express that goes before the seed esteem, with the intention of at the following timer beat, this original stone remains in that LFSR, and the procedure depends on deterministic seeds which venture into ATPG designs so 100% flaw inclusion can be accomplished. The calculation depends on the accompanying techniques: (1) produce ATPG designs for deficiencies that were not identified with pseudo-irregular examples and figure seeds for these examples, (2) when a seed is stacked into the LFSR, let the LFSR run in self-governing mode for at some point in light of the fact that there's an open door that some of the ATPG examples will drop more blames so a portion of the ATPG designs are not required, (3) as long as pseudoarbitrary examples don't recognize issues, the LFSR ought to be stacked with another example. This procedure depends on deterministic seeds which venture into ATPG designs so high deficiency inclusion can be accomplished and diminished the test length.

# 3.2.2 Roving STAR Approach

Typically testing happens inside the meandering STARs while the framework proceeds with activity in the rest of the bits of the FPGA. Originally Transparent ORCA 2C arrangement FPGA is utilized pro that arranging and execution of this BIST then finding; yet now this framework is accentuated and might remain related to some FPGA this highlights gradual RTR, for example, this Xilinx Virtex arrangement FPGA respectively.

In this ordinary activities of FPGAs, as various capacities will be arranged to FPGAs and the designed rationale will be lost when FPGAs are power off, an outer module outside of FPGA is utilized to execute the reconfiguration procedure. Such very controller is normally an inserted chip or microcontroller. It has some memory or uses additional memory, e.g., ROM, EEPROM, to store the setups for the application capacities, however in Roving STARs reached out to the test and analysis capacities. So this processor is likewise eluded as Test and Reconfiguration Controller (TREC) [18]. TREC controls the typical activity of FPGAs, yet additionally can access to BISTERs for testing and diagnosing. On the off chance that flaws are recognized, TREC begins the determination procedure e.g., if a shortcoming exists and found, when a similar part will be test next time, the TREC can skip it or test it practically as somewhat usable square (PUB), if there should arise an occurrence of utilitarian testing. At the point when the conventional arrangements experience flawed CLBs or interconnects, TREC decides to sidestep the damaged assets or supplant them with issue free ones.

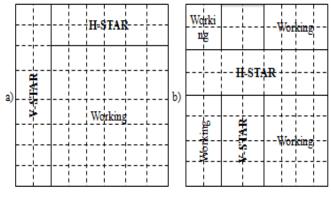

### 3.2.3 Roving STARs Assembly

Considering the assembly of STAR, Roving STAR[19] takes two areas of CLBs to shape a vertical STAR (V-STAR) and two lines of CLBs to outline a level STAR (H-STAR), similarly as the interconnect related with these CLBs. The lot number of segment or segment is for the symmetric idea. So when testing the CLBs in the STAR, an interconnection is attempted as well.as following Fig 3(a). It gives an underlying situation of STARs. The motivation to utilize two STARs, namely, H-STAR and V-STAR respectively, so the worldwide interconnect is normally spread into both the vertical and even course, both the V-STAR and H-STAR must be utilized simultaneously to test and finding. They likewise give basic highlights to determination, we will see in versatile analysis strategies and for testing methodology at the nearness of recently found deficiencies.

Figure 3 Roving STARs (a) Opening Location then (b) Thru Roving

A wandering development incorporates moving a cut of the system reason neighboring the STAR inside that present

STAR location then replicating this STAR method of reasoning inside that region deserted thru the structure basis respectively. That is represented with Figure.3 (b), afterwards unique wandering advance athwart of that V-STAR then unique meandering advance miserable of that H-STAR; in this meantime the past STAR regions are utilized for framework rationale.

In the wake of completing the main clearing, wandering alters to the contrary course, that is, left->right, up->down, right->left, down->up. Following this progression, one full even breadth of V-STAR and one full vertical leak of H-STAR are expected to test the whole FPGA. For a N\*N FPGA, a full range of one STAR requires N/2 positions; therefore, the allout number of meandering positions is N. The wandering procedure depends on run-time reconfiguration and it is constrained thru TREC respectively.

## 4. IMPLEMENTATION

## 4.1 Direct Test Relaxation

N-distinguish test unwinding procedure is principally used to decrease the test time since; it steps through exceptionally less exam examples to recognize deficiencies. Consequently it builds execution and force decrease. The adequacy of truly mindful N-distinguish (PAN-recognize) [20] test in identifying absconds influencing current plans has been exhibited utilizing both imperfection recreation and underway ASICs. The pertinence of a PAN-identify test set can be additionally improved by utilizing test unwinding. Test unwinding is a procedure of changing over a completely determined test set to an incompletely indicated (loose) one with however many unknown test-input esteems as could be expected under the circumstances.

The advantage of performing test unwinding originates from the adaptability of reassigning the unknown test input esteems for (1) test pressure, (2) decreasing influence caused during check test, (3) implanting tests to distinguish focused on flaws all the more frequently, and (4) improving tests to concentrate on other issue models. Yen-Tzu Lin, Emeka Ezekwe and Shawn Blanton have built up a truly mindful test unwinding (PATR) programming, where data gathered in test age or issue reproduction is abused for efficiently distinguishing testinputs that can be left vague (i.e., changed to a couldn't care less esteem). The nature of the casual test set is guaranteed by keeping up the PAN-distinguish inclusion of the first test sets.

## 4.2 Hybrid Algorithm

This paper likewise addresses cross breed calculation which is a mix of new vitality productive shortcoming open minded calculation [21] and new flexible deficiency lenient calculation [22] to give better blame inclusion and execution.

### 5. IMITATION OUTCOMES

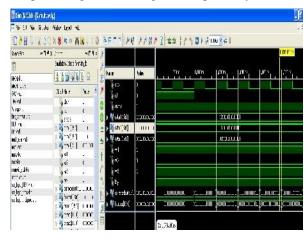

A reenactment consequence of the proposed adaptation to internal failure for NoC is introduced inside the kind of control plan in figure 4 then figure 5 respectively.

Figure 4 Timing Illustration for main output1

Figure 5 Timing Illustration for main output2

It is acquired utilizing Xilinx variant 12.1.In Fig.4 and Fig.5 Main yield has been gotten with the contribution of clk, reset, enable, and data in. Main Square is a mix of two sub squares NoC and BIST. NoC contains three sub modules, for example, Register (DEMUX), FIFO and Scheduler. BIST contains three sub squares, for example, Test design generator which is utilized to deliver true output. The resulting square called Circuit under test is generally used to make weakness yield from true output. The last and last square of BIST is Output reaction analyzer (ORA) which is utilized to get amended yield from shortcoming yield. The information data in is 16 pieces and Test design generator will deliver test design when reset gets zero. In this manner reseeding strategy produces rectified yield from broken.

# DEVICE UTILIZATION SUMMARY

| Device: Virtex(6vlx75tff484-3)                                    | Utilization In<br>Percentage |

|-------------------------------------------------------------------|------------------------------|

| Slice Logic Utilization:<br>Number of Slice Registers :-          | 1%                           |

| Number of Slice LUTs :-                                           | 2%                           |

| Number used as Logic :-                                           | 2%                           |

| Slice Logic Distribution:<br>Number of fully used LUT-FF Pairs :- | 29%                          |

| IO Utilization:<br>Number of Bonded IOBs :-                       | 62%                          |

| Specific Feature Utilization:<br>Number of BUFG/BUFGC TRLs :-     | 3%                           |

#### Table 1 Device application instant

In this work, contraption use expects a noteworthy activity since it will choose zone and power use of the assignment. Table1 shows the rundown of gadget usage that is number of registers, query tables, Flip-flops, input/yield squares and cradles (in rate) are utilized for this task.

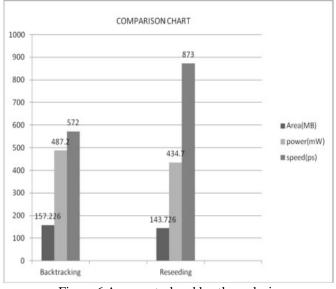

Figure 6 Area control and hustle analysis

Figure 6 present the examination of proposed reseeding calculation with the current Backtracking algorithm. These two calculations are contrasted and the principle three imperatives, for example, area, power and speed. In this work proposed calculation gives better outcome when contrasted and the backtracking algorithm. Hence proposed calculation give rapid and diminishes force and zone overhead.

#### 6. CONCLUSION

This paper has presented Fault flexibility and monetarily shrewd arrangement of NoC to help guaranteed throughput, power usage and diminishes zone. The proposed plan of NoC is totally actualized in Virtex-6 FPGA. The first segment of this work manages two strategies, for example, reseeding and meandering STAR to decide the deficiency in NoC. These strategies give great shortcoming inclusion yet it requires some investment for testing. So the second area of the venture presents another method and half and half calculation to diminish the test time. Consequently the exhibition and along these lines the shortcoming inclusion are improved hugely.

#### REFERENCES

- [1] Ababei, C. Katti, R. "Achieving network on chip fault tolerance by adaptive remapping",IEEE International Symposium on Parallel & Distributed Processing, May 2009.

- [2] Wen-Chung Tsai, Ying-Cherng Lan, Yu-Hen Hu, and Sao-Jie Chen, "Network on Chips: Structure and Design Methodologies" Journal of Electrical and Computer Engineering, 2012.

- [3] P. T. Wolkotte, G. J. M. Smit, G. K. Rauwerda, and L. T. Smit, "An energy- efficient reconfigurable circuit-switched network-onchip," in Proc. *IEEE Int. Parallel Distrib. Process. Symp*, 2005, p. 155a.

- [4] D.Wiklund and L. Dake, "SoCBUS: Switched network on chip for hard real time embedded systems," in Proc. Int. Parallel Distrib. Process.Symp. 2003, p. 8.

- [5] Pirretti Link Brooks , M. Pirretti , G. M. Link , R. R. Brooks , N. Vijaykrishnan , M. J. Irwin, "Fault Tolerant Algorithms for Network-On-Chip Interconnect", IEEE Computer Society Annual Symposium on VLSI Systems Design,2004.

- [6] L. Benini and G. De Micheli, "Networks on chips: A new SoC paradigm," *IEEE Computer*, vol. 35, no. 1, pp. 70–78, Jan. 2002

- [7] Charles Stroud, Matthew Lashinsky, Jeremy Nall, and John Emmert, Miron Abramovici, "On-Line BIST and Diagnosis of FPGA Interconnect Using Roving STARs" IEEE Symposium 0-7695-1290-9/01 2001.

- [8] Nan-Cheng Lai, Sying-Jyan Wang "A Reseeding Technique for LFSR Based BIST Application" IEEE Asian Test Symposium (ATS'02)1081-7735,2002.

- [9] Shivakumar Swaminathan and Krishnendu Chakrabarty " A Deterministic Scan-BIST Architecture with Application to Field esting of High-Availability Systems", Custom Integrated Circuits, IEEE conference on 2001.

- [10] Pooria M.Yaghini, Ashkan Eghbal, S.A. Asghari, and H.Pedram, "Power Comparison of an Asynchronous and Synchronous Network on Chip Router", 14th International CSI Computer Conference (CSICC'09) IEEE, 2009.

- [11] Ahmad .A,Al-Yamani and Edward J.McCluskey, "Built-In Reseeding for Serial BIST", IEEE VLSI Test Symposium (VTS.03),2003.

- [12] Yen-Tzu Lin, Emeka Ezekwe and Shawn Blanton http://www.ece.cmu.edu/~actl/research/n- detect\_relax.html

- [13] M. Abramovici, C. Stroud, S. Wijesuriya, and V. Verma, "Using roving STARs f or on-line testing and diagnosis of FPGAs in faulttolerant applications," in Proc. IEEE International Test Conference, pp. 973–982, 1999.

- [14] David Fick, Andrew DeOrio, Gregory Chen, Valeria Bertacco, Dennis Sylvester and David Blaauw, "A Highly Resilient Routing Algorithm for Fault Tolerant NoCs", Design, Automation & Test in Europe Conference, 2009

- [15] WU Yang, Abdullah Mumtaz, Hans- Joachim Wunderlich, "Online Test and Diagnosis", Seminar on Reconfigurable Hardware Architectures July 2012

- [16] D. Lattard, E. Beigne, F. Clermidy, Y. Durand, R. Lemaire, P. Vivet, and F. Berens, "A reconfigurable baseband platform based on an asynchronous network-on-chip," *IEEE J. Solid-State Circuits*, vol. 43, no.1, pp. 223–235, Jan. 2008

- [17] Nur A. Touba, Edward J. McCluskey "Bit-Fixing in Pseudorandom Sequences for Scan BIST" IEEE Transactions on computer-aided design of integrated circuits and systems, vol. 20, no. 4, April 2001

- [18] Phi-Hung Pham, Jongsun Park, Phuong Mau and Chulwoo Kim "Design and Implementation of Backtracking Wave- Pipeline Switch to Support Guaranteed Throughput in Network-on-Chip", IEEE Transactions on VLSI, Vol. 20, No. 2, Feb 2012

- [19] K. Goossens, J. Dielissen, and A. Radulescu, "Æthereal network on chip: Concepts, architectures, and implementations," *IEEE Des. Test. Comput.*, vol. 22, no. 5, pp. 414–421, 2005

- [20] R. Marculescu, U. Y. Ogras, P. Li- Shiuan, N. E. Jerger, and Y. Hoskote, "Outstanding research problems in NoC design: System, microarchitecture, and circuit perspectives," IEEE Trans. Computer Aided Design Integr. Circuits Syst., vol. 28, no. 1, pp. 3–21, Jan. 2009.

[21] Designing Fault Tolerant NoCs to Improve Reliability on SoCs / Arthur Pereira Frantz. – Porto Alegre: PPGC da UFRGS, Feb 2007.

Author

**Dr. S. Ravichandran**, M.C.A., M.Phil. M.Tech., ME., Ph.D., working as a HOD & Professor in Department of Computer Science at Annai Fathima College of Arts & Science, Madurai, Tamilnadu State, India. He has 23 years of teaching experiences in various Colleges. He has Published 29 papers in International journals, he has presented in 17 International Conferences & presented in 19 National Conferences at various Engineering Colleges. His areas of specialization are Cloud Computing, Artificial Intelligence,

Networks, software engineering and Compilers.